A senior design team from Rice University’s George R. Brown School of Engineering was recently selected as one of four finalists for the IEEE Circuits and Systems Society (CASS) Student Design Competition.

The team, representing Region 1-7 (USA and Canada), has been recognized for its project titled “Ghost in the Machine: High-Performance FPGA Implementation for Deep Learning Acceleration.” Team members include Maya Borowicz, Sophia Rohlfsen, Davis Jackson, Zhongqi Gao, Ares Lu, Winnie Fan and James Ding. The CASS Student Design Competition is a worldwide event where undergraduate students suggest and execute projects in electrical engineering and related areas with a focus on finding solutions to real-life problems based on circuits and systems.

Borowicz said the Rice team’s project addresses the need for more optimized training of machine learning models, which are the algorithms within some artificial intelligence systems.

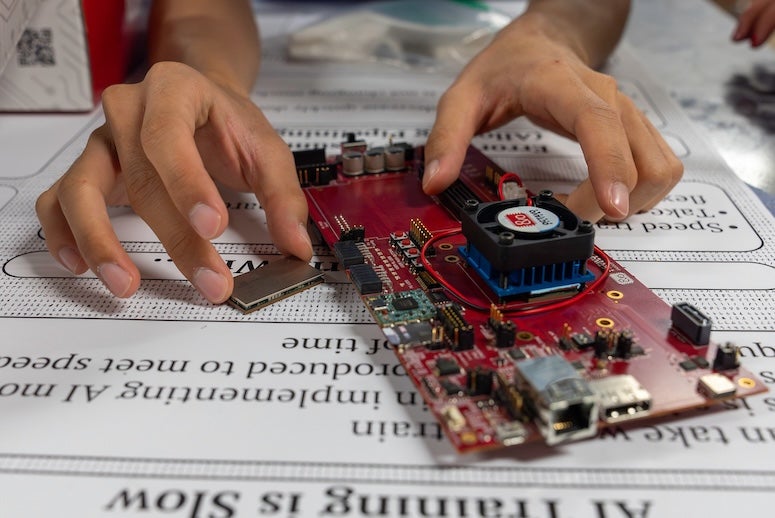

“Our approach is to focus on optimizing the computations necessary to train machine learning models,” said Borowicz, a senior majoring in electrical and computer engineering. “We approached this at a hardware level, performing the training using a programmable hardware called a field programmable gate array (FPGA). Addressing the training from hardware allows further optimization than using just software.”

FPGAs are integrated circuits often sold off the shelf. They provide customers the ability to reconfigure hardware to meet specific use requirements after the manufacturing process.

“What we’re really moving toward is a machine architecture that will have an initial programmation and then when it gets put in a new environment can learn and adapt — and do it with all of its own resources,” said Ray Simar, team mentor and professor in the practice of electrical and computer engineering. “That’s the ‘ghost’ in the machine. It’s the ability not just to interact but learn as it interacts.”

Simar said the project could provide greater machine learning capabilities for activity trackers like FitBit and others that keep track of everyday lifestyles.

“We started off at the beginning of this semester and I told the students this was going to be a little bit out there,” Simar said. “We were going to have to really understand these kinds of problems in the machine learning space at a level of detail that most software (engineers) probably aren’t really aware of.”

Simar said by the end of last semester, the model was getting three times the throughput improvement of other solutions.

“We’ll build on this project again next year,” he said. “I think we’re going to come up with some neat stuff to expand and improve how we can use machine learning in more spaces, and this project is really the seed for beginning to show some of that possibility. This was a project that I learned a lot from.”

Simar and students from the group will also present the project at the 38th IEEE International Parallel and Distributed Processing Symposium in San Francisco later this month.